# **OLED DISPLAY SPECIFICATION**

## 曜凌光電股份有限公司 Raystar Optronics, Inc.

T: +886-4-2565-0761 | F: +886-4-2565-0760

salescontact@raystar-optronics.com | www.raystar-optronics.com

#### **REX012864M**

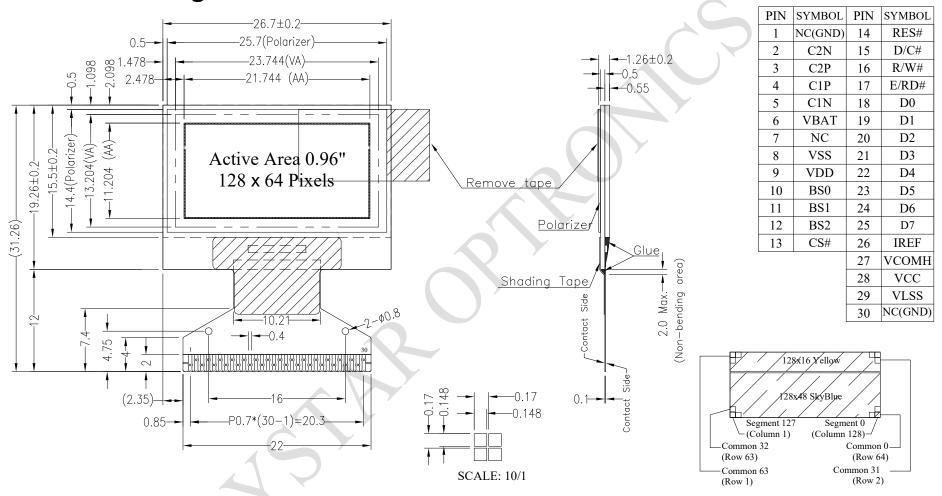

#### **General Specification**

■ Dot Matrix: 128 x 64 Dots

■ Module dimension: 26.7 × 19.26 × 1.26 (mm)

■ Active Area: 21.744 × 11.204 (mm)

■ Pixel Size: 0.148 × 0.148 (mm)

■ Pixel Pitch: 0.17 × 0.17 (mm)

■ Display Mode: Passive Matrix

■ Display Color: Monochrome

■ Drive Duty: 1/64 Duty

■ IC: SSD1306

■ Interface: 6800, 8080 ,SPI , I2C

■ SIZE: 0.96 inch

### **Interface Pin Function**

| No. | Symbol     | Function                                                                                                                                             |  |  |  |  |  |  |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|     | N.C.       | Reserved Pin (Supporting Pin)                                                                                                                        |  |  |  |  |  |  |

| 1   | (GND)      | The supporting pins can reduce the influences from stresses on the                                                                                   |  |  |  |  |  |  |

|     |            | function pins. These pins must be connected to external ground.                                                                                      |  |  |  |  |  |  |

| 2   | C2N        | Positive Terminal of the Flying Inverting Capacitor Negative Terminal of                                                                             |  |  |  |  |  |  |

| 3   | C2P        | the Flying Boost Capacitor The charge-pump capacitors are required                                                                                   |  |  |  |  |  |  |

| 5   | C1P<br>C1N | between the terminals. They must be floated when the converter is not used.                                                                          |  |  |  |  |  |  |

| 3   | CIN        | Power Supply for DC/DC Converter Circuit                                                                                                             |  |  |  |  |  |  |

| 6   | VBAT       | This is the power supply pin for the internal buffer of the DC/DC voltage                                                                            |  |  |  |  |  |  |

|     |            | converter. It must be connected to external source when the converter is                                                                             |  |  |  |  |  |  |

|     |            | used. It should be connected to VDD when the converter is not used.                                                                                  |  |  |  |  |  |  |

| 7   | NC         | NC<br>Ground of Logic Circuit                                                                                                                        |  |  |  |  |  |  |

| 8   | VSS        | This is a ground pin. It acts as a reference for the logic pins. It must be                                                                          |  |  |  |  |  |  |

|     | vss        | connected to external ground.                                                                                                                        |  |  |  |  |  |  |

| 9   | \/DD       | Power Supply for Logic                                                                                                                               |  |  |  |  |  |  |

| 9   | VDD        | This is a voltage supply pin. It must be connected to external source.                                                                               |  |  |  |  |  |  |

| 10  | BS0        | Communicating Protocol Select                                                                                                                        |  |  |  |  |  |  |

| 10  | 630        | These pins are MCU interface selection input. See the                                                                                                |  |  |  |  |  |  |

|     |            | following table:                                                                                                                                     |  |  |  |  |  |  |

| 11  | BS1        | BS0 BS1 BS2 I2C 0 1 0                                                                                                                                |  |  |  |  |  |  |

|     |            | 3-wire SPI 1 0 0                                                                                                                                     |  |  |  |  |  |  |

|     |            | 4-wire SPI 0 0 0                                                                                                                                     |  |  |  |  |  |  |

| 12  | BS2        | 8-bit 68XX Parallel                                                                                                                                  |  |  |  |  |  |  |

|     |            |                                                                                                                                                      |  |  |  |  |  |  |

| 13  | CS#        | Chip Select This pin is the chip select input. The chip is enabled for MCU                                                                           |  |  |  |  |  |  |

| 13  |            | communication only when CS# is pulled low.                                                                                                           |  |  |  |  |  |  |

|     |            | Power Reset for Controller and Driver                                                                                                                |  |  |  |  |  |  |

| 14  | RES#       | This pin is reset signal input. When the pin is low, initialization of the chip                                                                      |  |  |  |  |  |  |

|     |            | is executed.                                                                                                                                         |  |  |  |  |  |  |

|     |            | Data/Command Control                                                                                                                                 |  |  |  |  |  |  |

|     |            | This pin is Data/Command control pin. When the pin is pulled high, the                                                                               |  |  |  |  |  |  |

| 1   |            | input at D7~D0 is treated as display data.                                                                                                           |  |  |  |  |  |  |

|     | D/C#       | When the pin is pulled low, the input at D7~D0 will be transferred to the command register. For detail relationship to MCU interface signals, please |  |  |  |  |  |  |

| 15  |            | refer to the Timing Characteristics Diagrams.                                                                                                        |  |  |  |  |  |  |

|     |            | When the pin is pulled high and serial interface mode is selected, the data                                                                          |  |  |  |  |  |  |

|     |            | at SDIN is treated as data. When it is pulled low, the data at SDIN will be                                                                          |  |  |  |  |  |  |

|     |            | transferred to the command register. In I2C mode, this pin acts as SA0 for                                                                           |  |  |  |  |  |  |

|     |            | slave address selection.                                                                                                                             |  |  |  |  |  |  |

| 16    | R/W#        | Read/Write Select or Write This pin is MCU interface input. When interfacing to a 68XX-series microprocessor, this pin will be used as Read/Write (R/W#) selection input. Pull this pin to "High" for read mode and pull it to "Low" for write mode. When 80XX interface mode is selected, this pin will be the Write (WR#) input. Data write operation is initiated when this pin is pulled low and the CS# is pulled low.    |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17    | E/RD#       | Read/Write Enable or Read This pin is MCU interface input. When interfacing to a 68XX-series microprocessor, this pin will be used as the Enable (E) signal. Read/write operation is initiated when this pin is pulled high and the CS# is pulled low. When connecting to an 80XX-microprocessor, this pin receives the Read (RD#) signal. Data read operation is initiated when this pin is pulled low and CS# is pulled low. |

| 18~25 | D0~D7       | Host Data Input/Output Bus These pins are 8-bit bi-directional data bus to be connected to the microprocessor's data bus. When serial mode is selected, D1 will be the serial data input SDIN and D0 will be the serial clock input SCLK. When I2C mode is selected, D2 & D1 should be tired together and serve as SDAout & SDAin in application and D0 is the serial clock input SCL.                                         |

| 26    | IREF        | Current Reference for Brightness Adjustment This pin is segment current reference pin. A resistor should be connected between this pin and VSS. Set the current lower than 30uA.                                                                                                                                                                                                                                               |

| 27    | VCOMH       | Voltage Output High Level for COM Signal This pin is the input pin for the voltage output high level for COM signals. A capacitor should be connected between this pin and VSS.                                                                                                                                                                                                                                                |

| 28    | VCC         | Power Supply for OEL Panel This is the most positive voltage supply pin of the chip. A stabilization capacitor should be connected between this pin and VSS when the converter is used. It must be connected to external source when the converter is not used.                                                                                                                                                                |

| 29    | VLSS        | Ground of Analog Circuit This is an analog ground pin. It should be connected to VSS externally.                                                                                                                                                                                                                                                                                                                               |

| 30    | NC<br>(GND) | Reserved Pin (Supporting Pin) The supporting pins can reduce the influences from stresses on the function pins. These pins must be connected to external ground.                                                                                                                                                                                                                                                               |

#### **Contour Drawing**

The non-specified tolerance of dimension is  $\pm 0.3$ mm.

## **Absolute Maximum Ratings**

| Parameter                               | Symbol | Min  | Max  | Unit |

|-----------------------------------------|--------|------|------|------|

| Supply Voltage for Logic                | VDD    | 0    | 4    | V    |

| Charge Pump Regulator Supply<br>Voltage | VBAT   | -0.3 | 5.0  | V    |

| Supply Voltage for Display              | VCC    | 0    | 16.0 | V    |

| Operating Temperature                   | TOP    | -40  | +80  | °C   |

| Storage Temperature                     | TSTG   | -40  | +85  | °C   |

### **Electrical Characteristics**

#### **DC Electrical Characteristics**

| Item                                                                       | Symbol                | Condition | Min     | Тур | Max     | Unit |

|----------------------------------------------------------------------------|-----------------------|-----------|---------|-----|---------|------|

| Supply Voltage for Logic                                                   | VDD                   |           | 2.8     | 3.0 | 3.3     | V    |

| Supply Voltage for Display (Supplied Externally)                           | VCC                   | _         | 11.5    | 12  | 12.5    | V    |

| Charge Pump Regulator<br>Supply Voltage                                    | VBAT                  | _         | 3.0     | _   | 4.2     | V    |

| Charge Pump Output Voltage<br>for Display (Generated by<br>Internal DC/DC) | Charge<br>Pump<br>VCC | _         | 7.0     | 7.5 | _       | V    |

| Input High Volt.                                                           | VIH                   | _         | 0.8×VDD | _   | VDD     | V    |

| Input Low Volt.                                                            | VIL                   | _         | 0       | _   | 0.2×VDD | V    |

| Output High Volt.                                                          | VOH                   | _         | 0.9×VDD | _   | VDD     | V    |

| Output Low Volt.                                                           | VOL                   | _         | 0       | _   | 0.1×VDD | V    |

| Operating Current for VCC<br>(50% display ON)<br>(VCC Supplied Externally) | ICC                   | VCC =12V  | -       | 9   | 13.5    | mA   |

| 50% check Board operating<br>Current (VCC Generated by<br>Internal DC/DC)  | IBAT                  | _         | _       | 15  | 25      | mA   |