# ESMT

## 2x20W Stereo / 1x40W Mono Digital Audio Amplifier With 30 bands EQ and DRC Functions + 2Vrms Line Driver

## Features

- Supply voltage

3.3V for digital circuit

8V~26V for loudspeaker driver

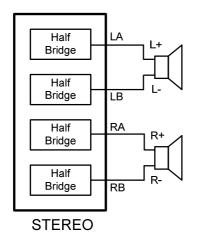

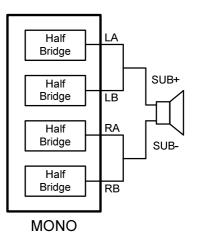

- Supports 2.0CH/Mono configuration

- Loudspeaker output power@12V for stereo

7W x 2CH into 8Ω <1% THD+N</li>

10W x 2CH into 4Ω <1% THD+N</li>

- Loudspeaker output power@18V for stereo 15W x 2CH into 8Ω <1% THD+N</li>

- Loudspeaker output power@24V for stereo 20W x 2CH into 8Ω <1% THD+N</li>

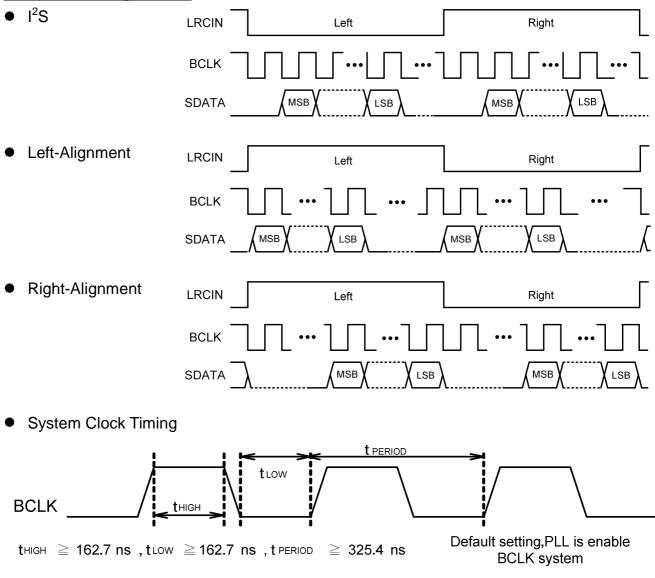

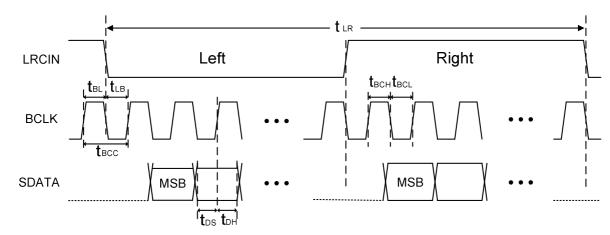

- 16/18/20/24-bits input with I<sup>2</sup>S, Left-alignment and Right-alignment data format

- Multiple sampling frequencies (Fs) 32kHz / 44.1kHz / 48kHz and 64kHz / 88.2kHz / 96kHz and 128kHz / 176.4kHz / 192kHz

- System clock = 64x, 128x, 192x, 256x, 384x, 512x, 576x, 768x, 1024x Fs

MCLK system:

- 64x~1024x Fs for 32kHz / 44.1kHz / 48kHz 64x~512x Fs for 64kHz / 88.2kHz / 96kHz 64x~256x Fs for 128kHz / 176.4kHz / 192kHz <u>BCLK system:</u>

64xFs for 32kHz / 44.1kHz / 48kHz 64xFs for 64kHz / 88.2kHz / 96kHz 64xFs for 128kHz / 176.4kHz / 192kHz

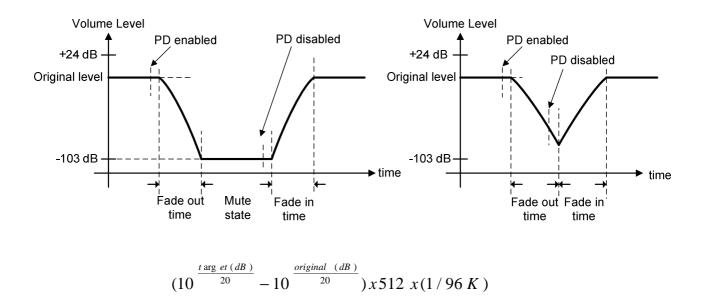

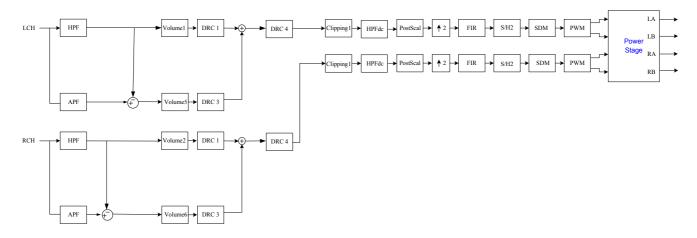

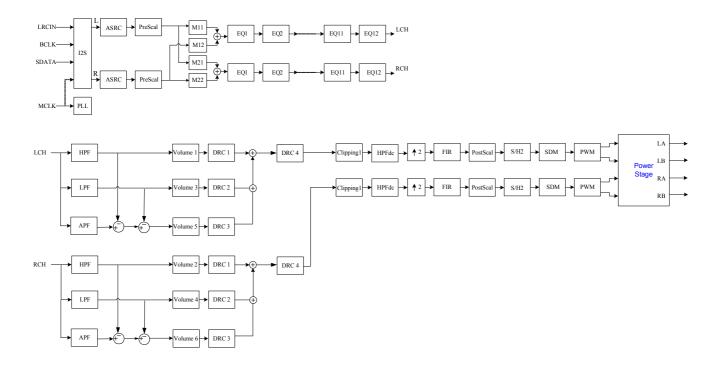

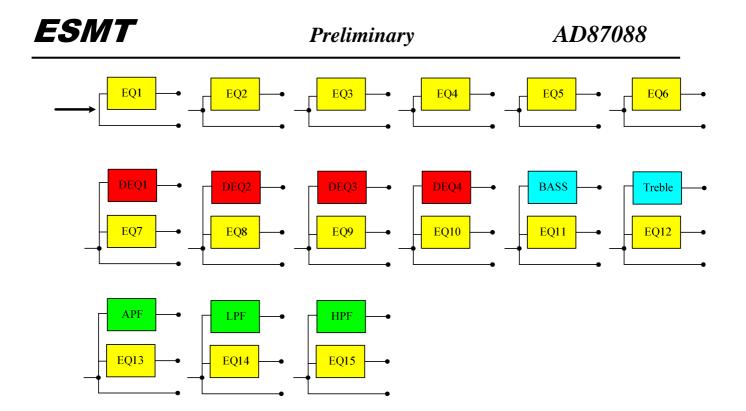

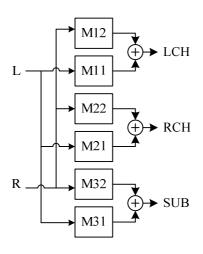

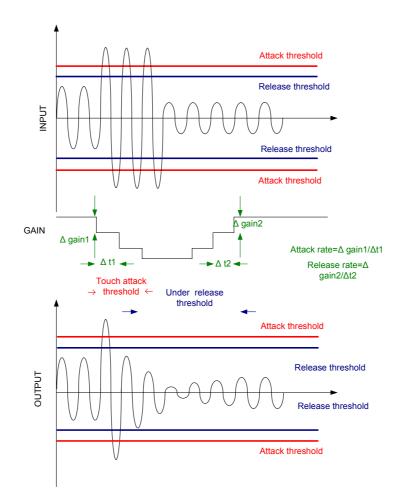

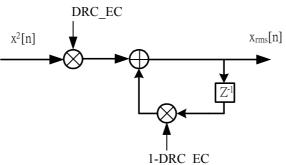

Sound processing including : 30 bands parametric speaker EQ Volume control (+24dB~-103dB, 0.125dB/step) Dynamic range control Three Band plus post Dynamic range control Power Clipping Programmed 3D surround sound Channel mixing Noise gate with hysteresis window Bass/Treble tone control DC-blocking high-pass filter Pre-scale/post-scale

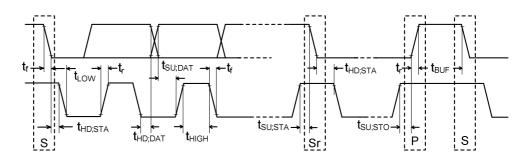

- Supports I<sup>2</sup>C control without clock

- I<sup>2</sup>C control interface with selectable device address

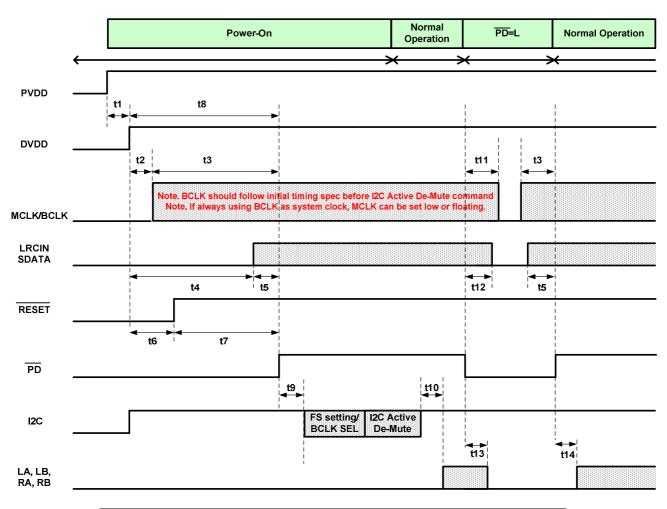

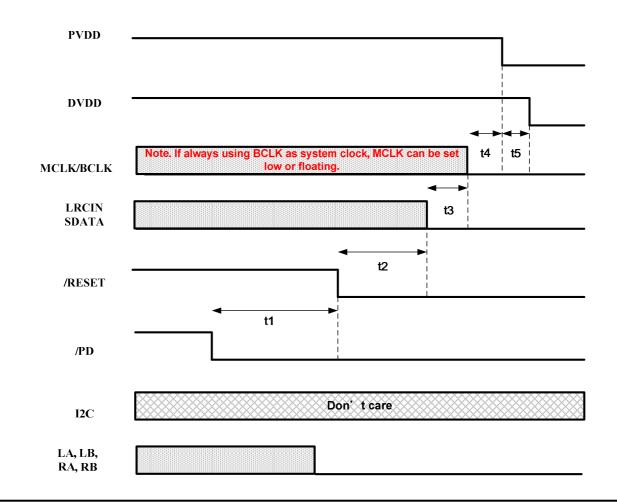

- Support hardware and software reset

- Internal PLL

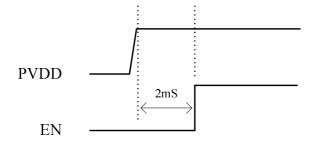

- Anti-pop design

- Level meter and power meter

- LV Under-voltage shutdown and HV Under-voltage detection

- Over voltage protection

- Short circuit and over-temperature protection

## **Applications**

- TV audio

- Boom-box, CD and DVD receiver, docking system

- Powered speaker

- Wireless audio

## **Description**

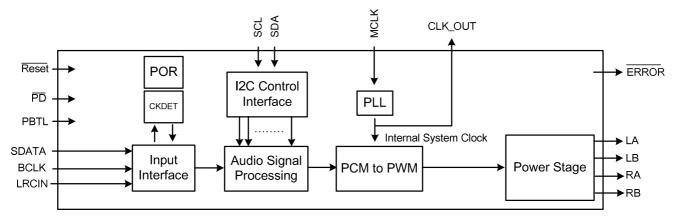

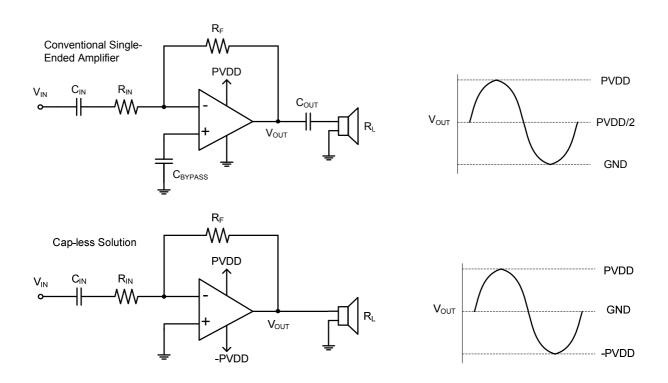

The AD87088 is an integrated audio system solution, embedding digital audio process, power stage amplifier and a stereo 2Vrms line driver. AD87088 is a digital audio amplifier capable of driving a pair of 8 $\Omega$ , 20W or a single 4 $\Omega$ , 40W operating at 24V supply. AD87088 provides advanced audio processing functions, such as volume control, 30 EQ bands, audio mixing, 3D surround sound and Dynamic Range Control (DRC). These are fully programmable via a simple I<sup>2</sup>C control interface. Robust protection circuits are provided to protect AD87088 from damage due to accidental erroneous operating condition. The full digital circuit design of AD87088 is more tolerant to noise and PVT (Process, Voltage, and Temperature) variation than the analog class-AB or class-D audio amplifier counterpart implemented by analog circuit design. AD87088 is pop free during instantaneous power on/off or mute/shut down switching because of its robust built-in anti-pop circuit.

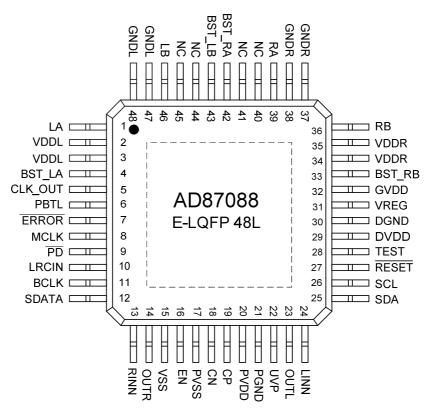

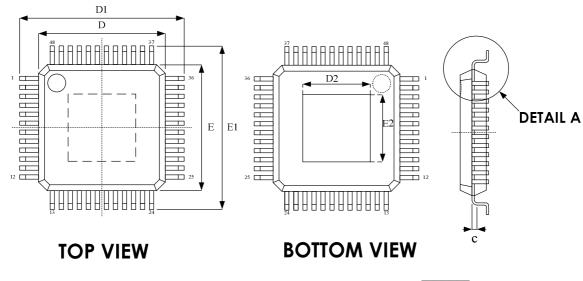

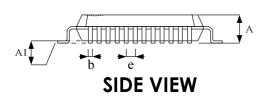

## Pin Assignment

## Pin Description (E-LQFP 48L)

| PIN | NAME    | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                               | CHARACTERISTICS                                                  |

|-----|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 1   | LA      | 0    | Left channel output A.                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                  |

| 2   | VDDL    | Р    | Left channel supply.                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                  |

| 3   | VDDL    | Р    | Left channel supply.                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                  |

| 4   | BST_LA  | Р    | Bootstrap supply for left channel output A.                                                                                                                                                                                                                                                                                                                                                                               |                                                                  |

| 5   | CLK_OUT | O/I  | PLL ratio setting pin during power up, this<br>pin is monitored on the rising edge of reset.<br>PMF register will be default set at 1 or 16<br>times PLL ratio.<br>High: PMF [3:0] = [0000], 1 time of PLL ratio<br>to avoid system BCLK over flow.<br>Low: PMF [3:0] = [0001], 16 times of PLL<br>ratio.<br>This pin could be clock output pin also<br>during normal operating if EN_CLK_OUT<br>register bit is enabled. | TTL output buffer, internal pull Low<br>with a 100Kohm resistor. |

| 6   | PBTL    | Ι    | Stereo/Mono configuration pin.<br>(Low: Stereo ; High: Mono)                                                                                                                                                                                                                                                                                                                                                              |                                                                  |

| 7         FROR         FROR         pin is a dual function pin. One is if C         This pin is monitored on the rising address setting during power up. The other edge of reset. A value of Low (15-KQ one is error status report (low active), It sets pull down) sets the if C device by register of A_SEL_FAULT at address           7         ERROR         I/O         one is error status report (low active), It sets pull down) sets the if C device by register of A_SEL_FAULT at address         address to Ko30 and a value of High (15-KQ pull up) sets it to 0x31.           8         MCLK         I         Master clock input.         Schmitt trigger TTL input buffer, internal pull Low with a 80Kohm resistor.           9         PpD         I         Power down, low active.         Schmitt trigger TTL input buffer, internal pull Low with a 80Kohm resistor.           10         LRCIN         I         Left/Right clock input (Fs).         Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.           11         BCLK         I         Bit clock input (64Fs).         Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.           12         SDATA         I         Serial audio data input.         Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.           13         RINN         I         Right output for line driver         Internal pull Low with an 80Kohm resistor.           14         OUTR         O         Right o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |       |     |                                                                     |                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|-----|---------------------------------------------------------------------|----------------------------------------------|

| 7       FROR       I/O       one is error status report (low active), It sets pull down) sets the I <sup>2</sup> C device address to 0x30 and a value of High 0x1C B[6] to enable it.       address to 0x30 and a value of High 0x1C B[6] to enable it.         8       MCLK       I       Master clock input.       Schmitt trigger TTL input buffer, internal pull Low with a 80Kohm resistor.         9       PD       I       Power down, low active.       Schmitt trigger TTL input buffer, internal pull High with a 330Kohm resistor.         10       LRCIN       I       Left/Right clock input (FS).       Schmitt trigger TTL input buffer, internal pull Low with a 80Kohm resistor.         11       BCLK       I       Bit clock input (FS).       Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.         12       SDATA       I       Bit clock input (64FS).       Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.         13       RINN       I       Right input for line driver       Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.         14       OUTR       O       Right output for line driver       Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.         15       VSS       P       Ground for line driver       Schmitt trigger TTL input buffer, connection for line driver         16       EN       I       Enable for line driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |       |     | $\overline{\text{ERROR}}$ pin is a dual function pin. One is $I^2C$ | This pin is monitored on the rising          |

| Image: Section of A_SEL_FAULT at address     address to 0x30 and a value of High (15-kΩ pull up) sets it to 0x31.       8     MCLK     I     Master clock input.     Schmitt trigger TTL input buffer, internal pull Low with a 80Kohm resistor.       9     PpD     I     Power down, low active.     Schmitt trigger TTL input buffer, internal pull ligh with a 330Kohm resistor.       10     LRCIN     I     Left/Right clock input (Fs).     Schmitt trigger TTL input buffer, internal pull Low with a 80Kohm resistor.       11     BCLK     I     Bit clock input (64Fs).     Schmitt trigger TTL input buffer, internal pull Low with a 80Kohm resistor.       12     SDATA     I     Serial audio data input.     Schmitt trigger TTL input buffer, internal pull Low with a 80Kohm resistor.       13     RINN     I     Right input for line driver     Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.       14     OUTR     O     Right output for line driver     Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.       15     VSS     P     Ground for line driver     Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.       16     EN     I     Right input for line driver     Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.       17     PVSS     P     Ground for line driver     Internal pull Low with an 80Kohm resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |       |     | address setting during power up. The other                          | edge of reset. A value of Low (15-k $\Omega$ |

| Image: Constraint of the set of the se  | 7  | ERROR | I/O | one is error status report (low active), It sets                    | pull down) sets the I <sup>2</sup> C device  |

| 8     MCLK     1     Master clock input.     Schmitt trigger TTL input buffer, internal pull Low with a 80Kohm resistor.       9     PD     1     Power down, low active.     Schmitt trigger TTL input buffer, internal pull High with a 330Kohm resistor.       10     LRCIN     1     Left/Right clock input (Fs).     Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.       11     BCLK     1     Left/Right clock input (Fs).     Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.       12     SDATA     1     Serial audio data input.     Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.       12     SDATA     1     Serial audio data input.     Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.       13     RINN     1     Right uput for line driver     Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.       14     OUTR     O     Right uput for line driver     Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.       15     VSS     P     Ground for line driver     Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.       16     EN     1     Enable for line driver     Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.       17     PVSS     P     Supply voltage for line driver     Schmitt trigger TT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |       |     | by register of A_SEL_FAULT at address                               | address to 0x30 and a value of High          |

| 8       MCLK       I       Master clock input.       Internal pull Low with a 80Kohm resistor.         9       Pp       I       Power down, low active.       Schmitt trigger TTL input buffer, internal pull High with a 330Kohm resistor.         10       LRCIN       I       Left/Right clock input (Fs).       Schmitt trigger TTL input buffer, internal pull Low with a 80Kohm resistor.         11       BCLK       I       Left/Right clock input (Fs).       Schmitt trigger TTL input buffer, internal pull Low with a 80Kohm resistor.         12       SDATA       I       Setral audio data input.       Schmitt trigger TTL input buffer, internal pull Low with a 80Kohm resistor.         13       RINN       I       Right input for line driver       Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.         14       OUTR       O       Right input for line driver       Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.         15       VSS       P       Ground for line driver       Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.         16       EN       I       Enable for line driver       Internal pull Low with an 80Kohm resistor.         17       PVSS       P       Supply voltage for line driver       Internal pull Low with an 80Kohm resistor.         18       CN       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       |     | 0x1C B[6] to enable it.                                             | (15-kΩ pull up) sets it to 0x31.             |

| Image: select of the select  |    |       |     |                                                                     | Schmitt trigger TTL input buffer,            |

| 9PDIPower down, low active.Schmitt trigger TTL input buffer,<br>internal pull High with a 330Kohm<br>resistor.10LRCINILeft/Right clock input (Fs).Schmitt trigger TTL input buffer,<br>internal pull Low with an 80Kohm<br>resistor.11BCLKILeft/Right clock input (Fs).Schmitt trigger TTL input buffer,<br>internal pull Low with an 80Kohm<br>resistor.12SDATAIBerial audio data input.Schmitt trigger TTL input buffer<br>internal pull Low with an 80Kohm<br>resistor.12SDATAISerial audio data input.Schmitt trigger TTL input buffer13RINNIRight input for line driverSchmitt trigger TTL input buffer14OUTRORight unput for line driverImage: Common comm                                                                                                                                                                                                                                                                                                                                                                                 | 8  | MCLK  | I   | Master clock input.                                                 | internal pull Low with a 80Kohm              |

| 9       PD       I       Power down, low active.       internal pull High with a 330Kohm resistor.         10       LRCIN       I       Left/Right clock input (Fs).       Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.         11       BCLK       I       Left/Right clock input (64Fs).       Schmitt trigger TTL input buffer, internal pull Low with an 80Kohm resistor.         12       SDATA       I       Serial audio data input.       Schmitt trigger TTL input buffer         13       RINN       I       Right input for line driver       Schmitt trigger TTL input buffer         14       OUTR       O       Right output for line driver       Image: Schmitt trigger TTL input buffer         15       VSS       P       Ground for line driver       Image: Schmitt trigger TTL input buffer         16       EN       I       Right output for line driver       Image: Schmitt trigger TTL input buffer         17       PVSS       P       Ground for line driver       Image: Schmitt trigger TTL input buffer         18       CN       I/O       Charge pump flying capacitor positive connection for line driver       Image: Schmitt trigger TTL input buffer         19       CP       I/O       Charge pump flying capacitor positive connection for line driver       Image: Schmitt trigger TTL input buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |       |     |                                                                     | resistor.                                    |

| Image: section of the section of th |    |       |     |                                                                     | Schmitt trigger TTL input buffer,            |

| 10LRCINILeft/Right clock input (Fs).Schmitt trigger TTL input buffer,<br>internal pull Low with an 80Kohm<br>resistor.11BCLKIBit clock input (64Fs).Schmitt trigger TTL input buffer,<br>internal pull Low with an 80Kohm<br>resistor.12SDATAISerial audio data input.Schmitt trigger TTL input buffer13RINNIRight input for line driverSchmitt trigger TTL input buffer14OUTRORight output for line driverImage: Schmitt trigger TTL input buffer15VSSPGround for line driverImage: Schmitt trigger TTL input buffer16ENIEnable for line driverImage: Schmitt trigger TTL input buffer18CNI/OCharge pump flying capacitor negative<br>connection for line driverImage: Schmitt trigger TTL input buffer19CPI/OCharge pump flying capacitor positive<br>connection for line driverImage: Schmitt trigger TTL input buffer20PVDDPSupply voltage for line driverImage: Schmitt trigger TTL input buffer21PGNDPGround for line driverImage: Schmitt trigger TTL input buffer22UVPIUnder voltage protection for line driverImage: Schmitt trigger TTL input buffer23OUTLOLeft output for Line driverImage: Schmitt trigger TTL input buffer24LINNILeft input for Line driverImage: Schmitt trigger TTL input buffer25SDAI/OI <sup>2</sup> C bi-directional serial data.Schmitt trigger TTL inpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9  | PD    | I   | Power down, low active.                                             | internal pull High with a 330Kohm            |

| 10LRCINILeft/Right clock input (Fs).internal pull Low with an 80Kohm<br>resistor.11BCLKIBit clock input (64Fs).Schmitt trigger TTL input buffer,<br>internal pull Low with an 80Kohm<br>resistor.12SDATAISerial audio data input.Schmitt trigger TTL input buffer13RINNIRight input for line driverSchmitt trigger TTL input buffer14OUTRORight output for line driverImage: Schmitt trigger TTL input buffer15VSSPGround for line driverImage: Schmitt trigger TTL input buffer16ENIEnable for line driverImage: Schmitt trigger TTL input buffer18CNI/OCharge pump flying capacitor negative<br>connection for line driverImage: Schmitt trigger TTL input buffer19CPI/OCharge pump flying capacitor positive<br>connection for line driverImage: Schmitt trigger TTL input buffer20PVDDPSupply voltage for line driverImage: Schmitt trigger TTL input buffer21PGNDPSupply voltage for line driverImage: Schmitt trigger TTL input buffer22UVPIUnder voltage protection for line driverImage: Schmitt trigger TTL input buffer23OUTLOLeft unput for Line driverImage: Schmitt trigger TTL input buffer24LINNILeft input for Line driverSchmitt trigger TTL input buffer25SDAI/OI <sup>2</sup> Cb-idriectional serial data.Schmitt trigger TTL input buffer26S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |       |     |                                                                     | resistor.                                    |

| Image: Answer and the second |    |       |     |                                                                     | Schmitt trigger TTL input buffer,            |

| 11BCLKIBit clock input (64Fs).Schmitt trigger TTL input buffer,<br>internal pull Low with an 80Kohm<br>resistor.12SDATAISerial audio data input.Schmitt trigger TTL input buffer13RINNIRight input for line driverSchmitt trigger TTL input buffer14OUTRORight output for line driverImage: Schmitt trigger TTL input buffer15VSSPGround for line driverImage: Schmitt trigger TTL input buffer16ENIEnable for line driverImage: Schmitt trigger TTL input buffer18CNI/OCharge pump flying capacitor negative<br>connection for line driverImage: Schmitt trigger TTL input buffer19CPI/OCharge pump flying capacitor positive<br>connection for line driverImage: Schmitt trigger TTL input buffer20PVDDPSupply voltage for line driverImage: Schmitt trigger TTL input buffer21PGNDPSupply voltage for line driverImage: Schmitt trigger TTL input buffer22UVPIUnder voltage protection for line driverImage: Schmitt trigger TTL input buffer23OUTLOLeft output for Line driverSchmitt trigger TTL input buffer24LINNILeft input for Line driverSchmitt trigger TTL input buffer25SDAI/OI <sup>2</sup> C serial clock input.Schmitt trigger TTL input buffer26SCLII <sup>2</sup> C serial clock input.Schmitt trigger TTL input buffer27RESETIReset, l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10 | LRCIN | I   | Left/Right clock input (Fs).                                        | internal pull Low with an 80Kohm             |

| 11BCLKIBit clock input (64Fs).internal pull Low with an 80Kohm<br>resistor.12SDATAISerial audio data input.Schmitt trigger TTL input buffer13RINNIRight input for line driverSchmitt trigger TTL input buffer14OUTRORight output for line driverImage: Schmitt trigger TTL input buffer15VSSPGround for line driverImage: Schmitt trigger TTL input buffer16ENIEnable for line driverImage: Schmitt trigger TTL input buffer17PVSSPSupply voltage for line driverImage: Schmitt trigger TTL input buffer18CNI/OCharge pump flying capacitor negative<br>connection for line driverImage: Schmitt trigger TTL input buffer19CPI/OCharge pump flying capacitor positive<br>connection for line driverImage: Schmitt trigger TTL input buffer20PVDDPSupply voltage for line driverImage: Schmitt trigger TTL input buffer21PGNDPGround for line driverImage: Schmitt trigger TTL input buffer22UVPIImage: Under voltage protection for line driverImage: Schmitt trigger TTL input buffer23OUTLOLeft input for Line driverSchmitt trigger TTL input buffer24LINNILeft output for Line driverSchmitt trigger TTL input buffer25SDAI/OI <sup>2</sup> C bi-directional serial data.Schmitt trigger TTL input buffer26SCLIIReset, low active. </td <td></td> <td></td> <td></td> <td></td> <td>resistor.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       |     |                                                                     | resistor.                                    |

| Image: Non-Section of the section o |    |       |     |                                                                     | Schmitt trigger TTL input buffer,            |

| 12SDATAISerial audio data input.Schmitt trigger TTL input buffer13RINNIRight input for line driver14OUTRORight output for line driver15VSSPGround for line driver16ENIEnable for line driver17PVSSPSupply voltage for line driver18CNI/OCharge pump flying capacitor negative<br>connection for line driver19CPI/OCharge pump flying capacitor positive<br>connection for line driver20PVDDPSupply voltage for line driver21PGNDPGround for line driver22UVPIUnder voltage protection for line driverInternally pulled high23OUTLOLeft output for Line driver24LINNILeft input for Line driverSchmitt trigger TTL input buffer25SDAI/OI²C bridirectional serial data.Schmitt trigger TTL input buffer26SCLII²C serial clock input.Schmitt trigger TTL input buffer27RESETIReset, low active.Schmitt trigger TTL input buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11 | BCLK  | Ι   | Bit clock input (64Fs).                                             | internal pull Low with an 80Kohm             |

| 13RINNIRight input for line driverSolution14OUTRORight output for line driverImage: Solution of the driver15VSSPGround for line driverImage: Solution of the driver16ENIEnable for line driverImage: Solution of the driver17PVSSPSupply voltage for line driverImage: Solution of the driver18CNI/OCharge pump flying capacitor negative connection for line driverImage: Solution of the driver19CPI/OCharge pump flying capacitor positive connection for line driverImage: Solution of the driver20PVDDPSupply voltage for line driverImage: Solution of the driver21PGNDPGround for line driverImage: Solution of the driver22UVPIUnder voltage protection for line driverImage: Solution of the driver23OUTLOLeft output for Line driverImage: Solution of the driver24LINNILeft input for Line driverSchmitt trigger TTL input buffer25SDAI/OI²C serial clock input.Schmitt trigger TTL input buffer26SCLIIReset, low active.Schmitt trigger TTL input buffer, internal pull High with a 330Kohm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |       |     |                                                                     | resistor.                                    |

| 14OUTRORight output for line driver15VSSPGround for line driver16ENIEnable for line driver17PVSSPSupply voltage for line driver18CNI/OCharge pump flying capacitor negative<br>connection for line driver19CPI/OCharge pump flying capacitor positive<br>connection for line driver20PVDDPSupply voltage for line driver21PGNDPGround for line driver22UVPIUnder voltage protection for line driver23OUTLOLeft output for Line driver24LINNILeft input for Line driver25SDAI/OI²C serial clock input.26SCLII²C serial clock input.27RESETIReset, low active.27RESETIReset, low active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12 | SDATA | I   | Serial audio data input.                                            | Schmitt trigger TTL input buffer             |

| 15VSSPGround for line driver16ENIEnable for line driver17PVSSPSupply voltage for line driver18CN $l/O$ Charge pump flying capacitor negative<br>connection for line driver19CP $l/O$ Charge pump flying capacitor positive<br>connection for line driver20PVDDPSupply voltage for line driver21PGNDPGround for line driver22UVPIUnder voltage protection for line driver23OUTLOLeft output for Line driver24LINNILeft input for Line driver25SDAI/O $l^2$ C bi-directional serial data.Schmitt trigger TTL input buffer26SCLI $l^2$ C serial clock input.Schmitt trigger TTL input buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13 | RINN  | Ι   | Right input for line driver                                         |                                              |

| 16ENIEnable for line driverImage: Constraint of the transmission of the transmission of the transmission of the transmission of transmissi                                     | 14 | OUTR  | 0   | Right output for line driver                                        |                                              |

| 17PVSSPSupply voltage for line driver18CNI/OCharge pump flying capacitor negative<br>connection for line driver19CPI/OCharge pump flying capacitor positive<br>connection for line driver20PVDDPSupply voltage for line driver21PGNDPSupply voltage for line driver22UVPIUnder voltage protection for line driver23OUTLOLeft output for Line driver24LINNILeft input for Line driver25SDAI/OI²C serial clock input.Schmitt trigger TTL input buffer26SCLII²C serial clock input.Schmitt trigger TTL input buffer27RESETIReset, low active.Schmitt trigger TTL input buffer,<br>internal pull High with a 330Kohm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15 | VSS   | Р   | Ground for line driver                                              |                                              |

| 18CNI/OCharge pump flying capacitor negative<br>connection for line driver19CPI/OCharge pump flying capacitor positive<br>connection for line driver20PVDDPSupply voltage for line driver21PGNDPGround for line driver22UVPIUnder voltage protection for line driver23OUTLOLeft output for Line driver24LINNILeft input for Line driver25SDAI/OI²C bi-directional serial data.Schmitt trigger TTL input buffer26SCLII²C serial clock input.Schmitt trigger TTL input buffer27RESETIReset, low active.Schmitt trigger TTL input buffer,<br>internal pull High with a 330Kohm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16 | EN    | I   | Enable for line driver                                              |                                              |

| 18CNI/Oconnection for line driver<br>connection for line driver19CPI/OCharge pump flying capacitor positive<br>connection for line driver20PVDDPSupply voltage for line driver21PGNDPGround for line driver22UVPIUnder voltage protection for line driver23OUTLOLeft output for Line driver24LINNILeft input for Line driver25SDAI/OI²C bi-directional serial data.Schmitt trigger TTL input buffer26SCLII²C serial clock input.Schmitt trigger TTL input buffer27RESETIReset, low active.Schmitt trigger TTL input buffer,<br>internal pull High with a 330Kohm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17 | PVSS  | Р   | Supply voltage for line driver                                      |                                              |

| Image: Connection for line driverConnection for line driver19CPI/OCharge pump flying capacitor positive<br>connection for line driverImage: Charge pump flying capacitor positive<br>connection for line driver20PVDDPSupply voltage for line driverImage: Charge pump flying capacitor positive<br>connection for line driver21PGNDPSupply voltage for line driverImage: Charge pump flying capacitor positive<br>connection for line driver22UVPIGround for line driverInternally pulled high23OUTLOLeft output for Line driverImage: Charge pump flying capacitor positive<br>connection for line driver24LINNILeft input for Line driverSchmitt trigger TTL input buffer25SDAI/OI²C serial clock input.Schmitt trigger TTL input buffer26SCLIIReset, low active.Schmitt trigger TTL input buffer,<br>internal pull High with a 330Kohm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18 | CN    | 1/0 | Charge pump flying capacitor negative                               |                                              |

| 19CPI/Oconnection for line driver20PVDDPSupply voltage for line driver21PGNDPGround for line driver22UVPIUnder voltage protection for line driver23OUTLOLeft output for Line driver24LINNILeft input for Line driver25SDAI/OI²C bi-directional serial data.Schmitt trigger TTL input buffer26SCLII²C serial clock input.Schmitt trigger TTL input buffer27RESETIReset, low active.Schmitt trigger TTL input buffer,<br>internal pull High with a 330Kohm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10 | CN    | 1/0 | connection for line driver                                          |                                              |

| 20PVDDPSupply voltage for line driver21PGNDPGround for line driver22UVPIUnder voltage protection for line driver23OUTLOLeft output for Line driver24LINNILeft input for Line driver25SDAI/OI²C bi-directional serial data.26SCLII²C serial clock input.27RESETIReset, low active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10 | CP    | 1/0 | Charge pump flying capacitor positive                               |                                              |

| 21PGNDPGround for line driver22UVPIUnder voltage protection for line driverInternally pulled high23OUTLOLeft output for Line driverInternally pulled high24LINNILeft input for Line driverImage: Schwitt trigger TTL input buffer25SDAI/OI²C bi-directional serial data.Schmitt trigger TTL input buffer26SCLII²C serial clock input.Schmitt trigger TTL input buffer27RESETIReset, low active.Schmitt trigger TTL input buffer,<br>internal pull High with a 330Kohm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19 | Cr    | 1/0 | connection for line driver                                          |                                              |

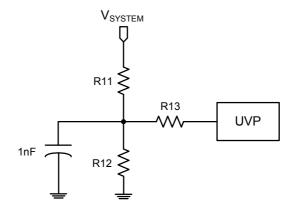

| 22UVPIUnder voltage protection for line driverInternally pulled high23OUTLOLeft output for Line driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20 | PVDD  | Р   | Supply voltage for line driver                                      |                                              |

| 23       OUTL       O       Left output for Line driver         24       LINN       I       Left input for Line driver         25       SDA       I/O       I <sup>2</sup> C bi-directional serial data.       Schmitt trigger TTL input buffer         26       SCL       I       I <sup>2</sup> C serial clock input.       Schmitt trigger TTL input buffer         27       RESET       I       Reset, low active.       Schmitt trigger TTL input huffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21 | PGND  | Р   | Ground for line driver                                              |                                              |

| 24       LINN       I       Left input for Line driver         25       SDA       I/O       I <sup>2</sup> C bi-directional serial data.       Schmitt trigger TTL input buffer         26       SCL       I       I <sup>2</sup> C serial clock input.       Schmitt trigger TTL input buffer         27       RESET       I       Reset, low active.       Schmitt trigger TTL input buffer, internal pull High with a 330Kohm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22 | UVP   | Ι   | Under voltage protection for line driver                            | Internally pulled high                       |

| 25       SDA       I/O       I <sup>2</sup> C bi-directional serial data.       Schmitt trigger TTL input buffer         26       SCL       I       I <sup>2</sup> C serial clock input.       Schmitt trigger TTL input buffer         27       RESET       I       Reset, low active.       Schmitt trigger TTL input buffer, internal pull High with a 330Kohm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23 | OUTL  | 0   | Left output for Line driver                                         |                                              |

| 26       SCL       I       I <sup>2</sup> C serial clock input.       Schmitt trigger TTL input buffer         27       RESET       I       Reset, low active.       Schmitt trigger TTL input buffer, internal pull High with a 330Kohm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24 | LINN  | I   | Left input for Line driver                                          |                                              |

| 27     RESET     I     Reset, low active.     Schmitt trigger TTL input buffer, internal pull High with a 330Kohm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25 | SDA   | I/O | I <sup>2</sup> C bi-directional serial data.                        | Schmitt trigger TTL input buffer             |

| 27   RESET   I   Reset, low active.   internal pull High with a 330Kohm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26 | SCL   | I   | I <sup>2</sup> C serial clock input.                                | Schmitt trigger TTL input buffer             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |     |                                                                     | Schmitt trigger TTL input buffer,            |

| resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27 | RESET | I   | Reset, low active.                                                  | internal pull High with a 330Kohm            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |     |                                                                     | resistor.                                    |

## Preliminary

| <b></b> |        |   |                                              | ĩ |

|---------|--------|---|----------------------------------------------|---|

| 28      | TEST   | I | This pin must connect to GND.                |   |

| 29      | DVDD   | Р | Digital Power.                               |   |

| 30      | DGND   | Р | Digital Ground.                              |   |

| 31      | VREG   | 0 | 1.8V Regulator voltage output.               |   |

| 32      | GVDD   | 0 | 5V Regulator voltage output. This pin must   |   |

| 32      | GVDD   | 0 | not be used to drive external devices.       |   |

| 33      | BST_RB | Р | Bootstrap supply for right channel output B. |   |

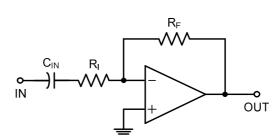

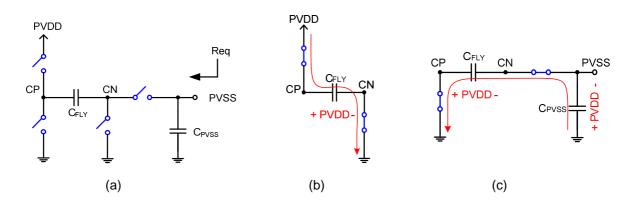

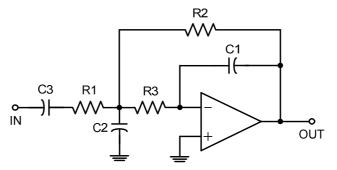

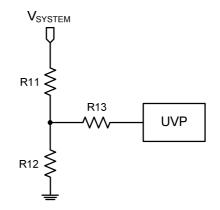

| 34      | VDDR   | Р | Right channel supply.                        |   |